GEPPCBug Firmware Package User’s Manual Parts 1 & 2

8. Calculate the external bus clock speed of the MPU.

9. Delay for 750 milliseconds.

10. Determine the CPU board type.

11. Size the local read/write memory (i.e., DRAM).

12. Initialize the read/write memory controller

13. Set base address of memory to $00000000.

14. Retrieve the speed of read/write memory from NVRAM.

15. Initialize read/write memory controller with the speed of

read/write memory.

16. Retrieve the speed of read only memory (i.e., FLASH) from

NVRAM.

17. Initialize read only memory controller with the speed of read

only memory.

18. Enable the MPU's instruction cache.

19. Copy the MPU's exception vector table from $FFF00000 to

$00000000.

20. Initialize the SIO (PC87303/PC87307/PC87308) resources'

base addresses for boards that have the SIO device.

21. Initialize the Z8536 device if the board has the device.

22. Verify MPU type.

23. Enable the super-scalar feature of the MPU (boards with

MPC604-type chips only).

24. Initialize the Keyboard Controller

(PC87303/PC87307/PC87308) for boards that have the

device.

25. Determine the debugger's Console/Host ports, and initialize

the appropriate UART and Graphic devices.

26. Display the debugger's copyright message.

27. Display any hardware initialization errors that may have

occurred.

28. Checksum the debugger object, and display a warning

message if the checksum failed to verify.

29. Display the amount of local read/write memory found.

30. Verify the configuration data that is resident in NVRAM,

and display a warning message if the verification failed.

31. Calculate and display the MPU clock speed. Verify that the

MPU clock speed matches the configuration data, and

display a warning message if the verification fails.

32. Display the BUS clock speed. Verify that the BUS clock speed

matches the configuration data, and display a warning

message if the verification fails.

33. For boards that have a Keyboard Controller display

initialization errors that have occurred.

34. Probe PCI bus for supported Network devices.

35. Probe PCI bus for supported Mass Storage devices.

36. Initialize the memory/IO addresses for the supported PCI

bus devices.

37. Execute self-test, if configured.

38. Extinguish the board fail LED, if there are no self-test failures

or initialization/configuration errors.

39. Execute the configured boot routine, either ROMboot,

Autoboot, or Network Autoboot. (PowerPlus architecture

boards do not execute a configured boot routine.)

40. Execute the user interface (i.e., the PPC1-Bug> or

PPC1-Diag> prompt).

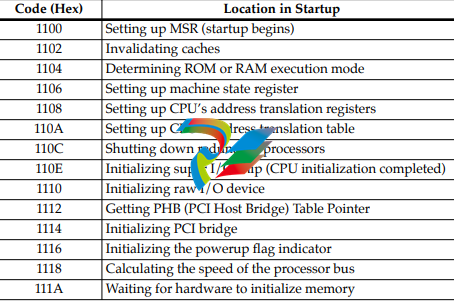

LED/Serial Startup Diagnostic Codes

These codes are displayed on seven-segment LEDs at key points in

the initialization of the hardware devices. Should the debugger fail

to come up to a prompt, the last code displayed will indicate how

far the initialization sequence had progressed before stalling. The

serial port version of the startup codes is enabled by an ENV

parameter:

Serial Startup Code Master Enable [Y/N]=N?

Under normal conditions, the startup sequence begins at 0x1100

and continues to the PPC1-Bug> prompt just after 0x11D4. RAM

initialization problems may cause the startup sequence to terminate

at the : (RawBug) prompt just after 0x11D8 instead.

The operating system boot sequence begins at 0x11E0 with the

creation of residual data and continues to 0x11EC just before

execution is passed to the boot image. The OS may have its own

LED codes which are displayed after 0x11EC.

A line feed can be inserted after each serial code is displayed to

prevent it from being overwritten by the next code. This is also

enabled by an ENV parameter:

Serial Startup Code LF Enable [Y/N]=N?

The following firmware codes are always sent to 7-segment LEDs

located at ISA I/O address 0x8C0. These codes can also be sent to

the debugger serial port if the ENV parameter “Serial Startup Code

Master Enable” is set to ‘Y’. The list of LED/serial codes follows.

Table 1-1. LED/Serial Startup Diagnostic Codes