ABBAdvant Controller 31 40 & 50 Series

applications and ensure all the basic PLC functions. It is developed with the AC31GRAF

software. After being translated into instructions understable by the central unit it is loaded in

RUN or STOP mode into the SRAM and then saved from the SRAM to the Flash EPROM.

Thereby, at each program launch the user program, saved in the Flash EPROM, is copied to

the SRAM for processing by the microprocessor (Figure 1-3).

The structure of the system program memory, the user program, the inputs / outputs and

internal variables are described in the annex (mapping).

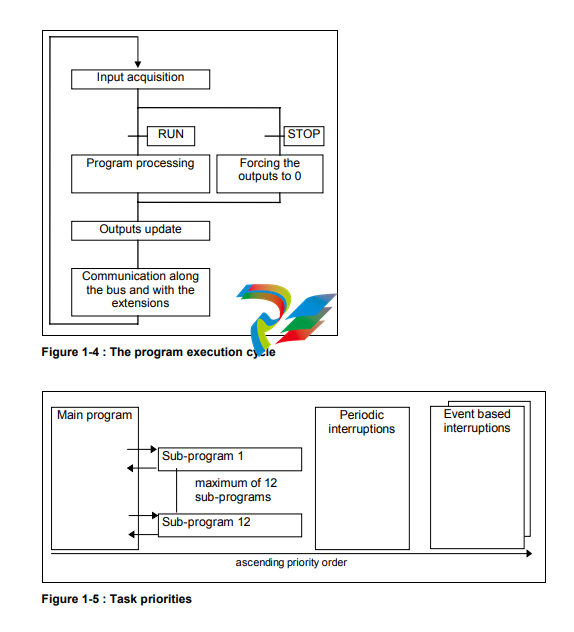

The central unit microprocessor ensures the cyclic execution of the system as shown in

Figure 1-4.

The internal processing:

- PLC monitoring and control

- and processing requests from the terminal operator,

is executed in parallel with the previously described cycle.

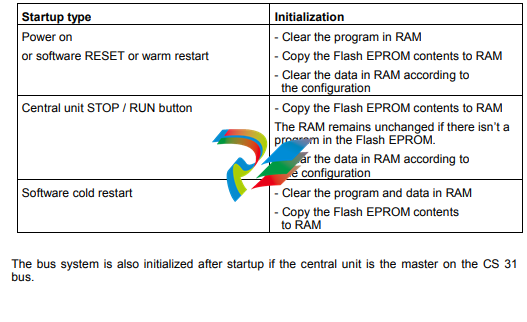

The main program is processed sequentially. It may call up to a maximum of 12 sub-programs.

Each sub-program may be called numerous times in the main program.

Three types of interruptions may be executed parallel to the main program:

- A cyclic interruption

- A warning interruption triggered by an event on the I 62.03 input

- A warning interruption triggered by an event on the I 62.02 input

The interruptions have priority over the main program execution. If all three interruptions are

triggered simultaneously then the interruption triggered by I 62.03 has priority over the I 62.02

input interruption which in turn has priority over the cyclic interruption. Once an interruption has

been launched it cannot be interrupted by another (Figure 1-5).

The execution duration of a cycle (bus cycle + program cycle) is controlled by the central unit.

Any excess of the cycle time defined by the user in AC31GRAF is signaled by the ERR Led, at

the front of the central unit, as of the first program cycle.

3.3. Bus transmission

The master central unit manages the transmission of messages to the various slaves over a

RS485 serial liaison.

The messages are transmitted under the following format:

- Request from the master central unit:

address data CRC8

- Request from the remote units:

start data CRC8

The messages always end with an end of frame control: checksum CRC8.

The length of the exchanged frames depends on the type of unit. Frames exchanged with an

analog unit are the longest

The central unit interrogates the remote units in order to establish an initial image of the

system configuration during initialization.

The remote units are then interrogated with each bus cycle. This enables the recognition of

newly added or removed remote units and the updating of the diagnosis information.

If the central unit receives a message indicating a CRC8 error it will not be signaled

immediately and the frame will not be taken into account. After nine consecutive transmission

errors a “bus error” is signaled by the central unit. The bus error is also signaled to the remote

units after a 250 ms time-out.

3.4. Refresh times / reply times

Bus refresh times and central unit reply times depend on the system configuration, the number

and the type of remote units on the CS 31 bus. The bus refresh and the user programs are

executed in series.

3.4.1. Bus refresh times

The bus refresh time corresponds to the transmission time over the bus. The calculation

corresponds to the addition of all the communication times of the remote units on the bus and

the base time of the master central unit which is 2 ms.

3.4.2. Central unit reply times

The central unit reply time corresponds to the time taken to activate an output after the

activation of an input.

The maximum reply time is obtained by adding the filtering time of the input, the bus refresh

time, the delay time for the output and twice the cycle time.

The filtering time for an input on the 40 and 50 series is 5 ms.

The delay time for a transistor output is considered as null in milliseconds and the delay time

for a relay output is 6 ms.

Comment:

The inputs / outputs of central units and their extensions can be accessed, for rapid

processing, independently of the cycle time with the user program functions DI and DO (see

chapter 6).

The cycle time calculation is given in chapter 5 at the cycle time configuration level as well as

the communication times of each unit for the bus transmission times calculation.

3.5. Power on / program launch

The central unit executes a complete series of auto tests at each startup. The program can

only be launched if no errors have been detected.

The auto tests verify the following:

- the program syntax,

- the data transmission,

- the status of the extensions,

- the status of the remote units if there is a master central unit,

- the startup conditions (reset or not of internal memories).

The central unit initialization depends on the startup type:

3.6. Power cuts or drops

The 40/50 series central unit disposes of a time delay in order to save the necessary

information for the next startup should there be a power drop or cut.

Saving program internal data is only possible on the 40/50 series central unit which possesses

an battery. Prior configuration of the central unit is required to save all or part of the data (see

chapter 5). If the configuration is absent then all functions and internal data will be reset to 0.

.png)