EMERSONMVME55006E Single-Board Computer Installation and Use

in J3.

8. Insert the four screws (Phillips type) through the holes at the corners of

PMCspanx6E-010 and into the standoffs on the primary PMCspanx6E-002. Tighten

screws securely.

The screws have two different head diameters. Use the screws with the smaller

heads on the standoffs next to VMEbus connectors P1 and P2.

You are now ready to install the module into the VME chassis. Follow the procedure, Installing

the Board on page 33.

Installing the Board

Procedure

Use the following steps to install the MVME5500 into your computer chassis.

1. Attach an ESD strap to your wrist. Attach the other end of the ESD strap to an

electrical ground (refer to Unpacking Guidelines). The ESD strap must be secured

to your wrist and to ground throughout the procedure.

2. Remove any filler panel that might fill that slot.

3. Install the top and bottom edge of the MVME5500 into the guides of the chassis.

Only use injector handles for board insertion to avoid damage/deformation to the

front panel and/or PCB.

4. Ensure that the levers of the two injector/ejectors are in the outward position.

5. Slide the MVME5500 into the chassis until resistance is felt.

6. Simultaneously move the injector/ejector levers in an inward direction.

7. Verify that the MVME5500 is properly seated and secure it to the chassis using the

two screws located adjacent to the injector/ejector levers.

8. Connect the appropriate cables to the MVME5500.

1.9.1 Connection to Peripherals

When the MVME5500 is installed in a chassis, you are ready to connect peripherals and apply

power to the board.

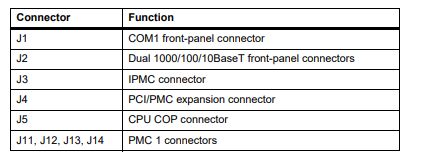

Figure 1-1 on page 20 shows the locations of the various connectors while Table 1-3 lists them

for you. Refer to Chapter 5, Connector Pin Assignments for the pin assignments of the

connectors listed below.

If a PMC module is plugged into PMC slot 1, the memory mezzanine card cannot be used

because the PMC module covers the memory mezzanine connector.

Figure 1-17 Installation into a Typical VME Chass

Completing the Installation

Verify that hardware is installed and the power/peripheral cables connected are appropriate for

your system configuration.

Replace the chassis or system cover, reconnect the system to the AC or DC power source, and

turn the equipment power on.

1.10 Startup and Operation

This section gives you information about:

z The power-up procedure

z Switches and indicators

1.11 Applying Power

After you verify that all necessary hardware preparation is complete and all connections are

made correctly, you can apply power to the system.

When you are ready to apply power to the MVME5500:

z Verify that the chassis power supply voltage setting matches the voltage present in the

country of use (if the power supply in your system is not auto-sensing)

z On powering up, the MVME5500 brings up the MotLoad prompt, MVME5500>

1.12 Switches and Indicators

The MVME5500 board provides a single push button switch that provides both Abort and Reset

(ABT/RST) functions. When the switch is depressed for less than three seconds, an abort

interrupt is generated to the processor. If the switch is held for more than three seconds, a

board hard reset is generated.

The MVME5500 has two front-panel indicators:

z BFL, software controlled. Asserted by firmware (or other software) to indicate a

configuration problem (or other failure).

z CPU, connected to a CPU bus control signal to indicate bus activity.

The following table describes these indicators:

Table 1-4 Front-Panel LED Status Indicators

Function Label Color Description

CPU Bus Activity CPU Green CPU bus is busy.

Board Fail BFL Yellow Board has a failure.

Functional Description

2.1 Overview

This chapter describes the MVME5500 on a block diagram level.

2.2 Block Diagram

Table 2-1 shows a block diagram of the overall board architecture.

Figure 2-1 Block Diagram

Features

The following table lists the features of the MVME5500.

Table 2-1 MVME5500 Features Summary

Processor

The MVME5500 supports the MPC7457 processor in the 483-pin CBGA package. The

processor consists of a processor core, an internal 256KB L2 and an internal L3 tag and

controller, which supports a backside L3 cache.

2.5 L3 Cache

The MVME5500 uses two 8Mb DDR synchronous SRAM devices for the processor’s L3 cache

data SRAM. This gives the processor a total of 2MB of L3 cache. These SRAM devices require

a 2.5V core voltage. The MVME5500 provides 1.5V as the SRAM I/O voltage. The L3 bus

operates at 200 MHz.

2.6 System Controller

The GT-64260B system controller for PowerPC architecture processors is a single chip solution

that provides the following features:

z A 64-bit interface to the CPU bus

z A 64-bit SDRAM interface

z A 32-bit generic device interface for Flash, etc.

z Two 64-bit, 66 MHz PCI bus interfaces

z Three 10/100Mb Ethernet MAC ports (two ports not used)

z A DMA engine for moving data between the buses

z An interrupt controller

z An I2C device controller

z PowerPC bus arbiter

z Counter/timers