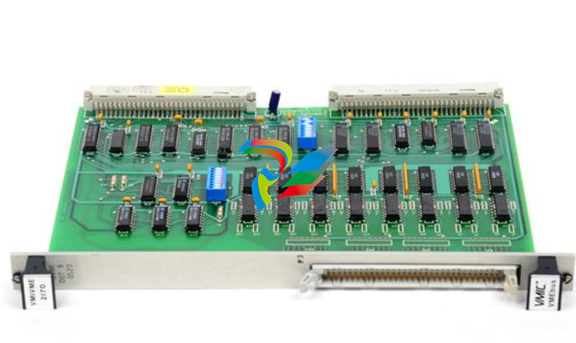

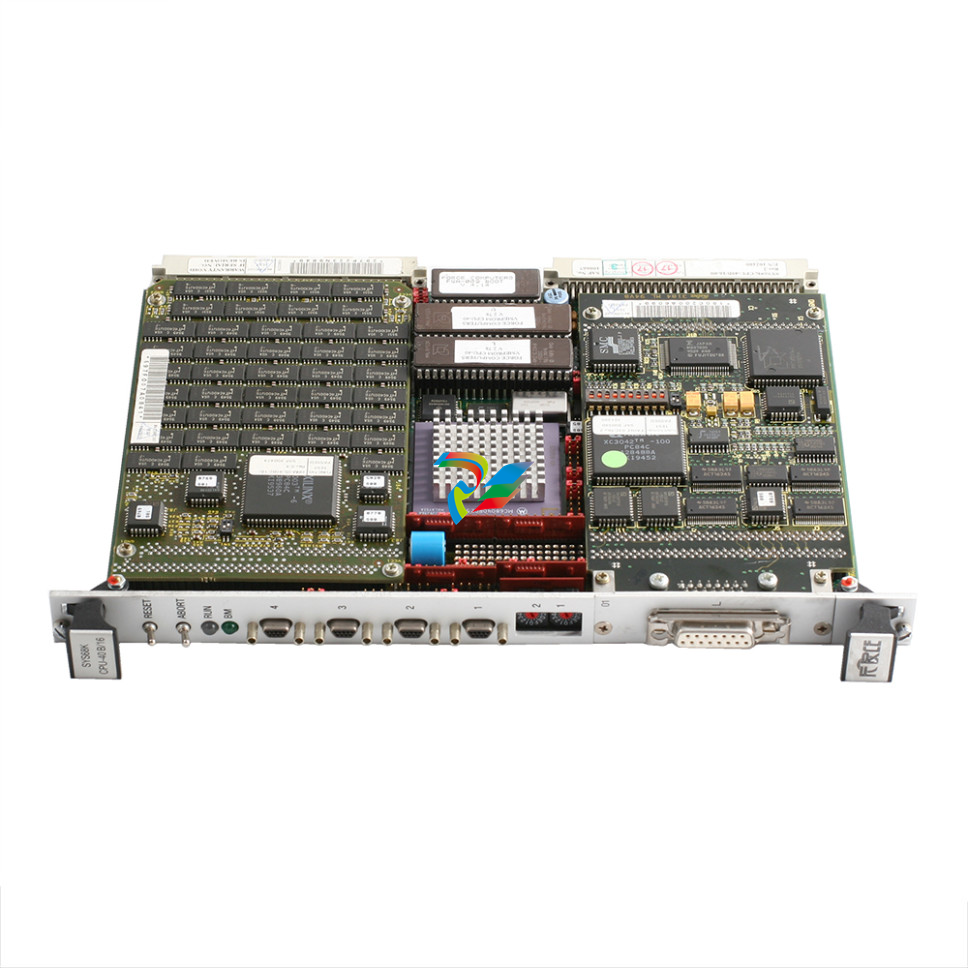

GE VMIVME-5576 Fiber-Optic Reflective Memory with Interrupts

VMIVME-5576

Fiber-Optic Reflective Memory with Interrupts

High-speed, easy-to-use fiber-optic network (170 Mbaud serially)

Data written to memory in one node is also written to memory in all nodes on

the network

Up to 2.000 m between nodes and up to 256 nodes

Data transferred at 6.2 Mbyte/s without redundant transfer

Data transferred at 3.2 Mbyte/s with redundant transfer

Any node on the network can generate an interrupt in any other node on the

network or in all network nodes with a single command

Error detection

Redundant transmission mode for suppressing errors

No processor overhead

No processor involvement in the operation of the network

Up to 1 Mbyte of Reflective Memory

A24:A32:D32:D16:D8 memory access

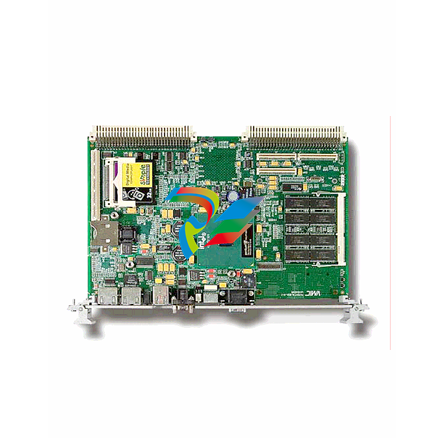

Single 6U VMEbus board

INTRODUCTION

VMIVME-5576 is a

high-performance, multidrop VME-to-VME network. Data is

transferred by writing to on-board global RAM. The data is

automatically sent to the location in memory on all Reflective

Memory boards on the network.

PRODUCT OVERVIEW

—

The Reflective Memory

concept provides a very fast and efficient way of sharing data

across distributed computer systems.

VMIC’s VMIVME-5576 Reflective Memory interface

allows data to be shared between up to 256 independent

systems (nodes) at rates up to 6.2 Mbyte/s. Each Reflective

Memory board may be configured with 256 Kbyte to 1 Mbyte

of on-board SRAM. The local SRAM provides fast Read

access times to stored data. Writes are stored in local SRAM

and broadcast over a high-speed fiber-optic data path to other

Reflective Memory nodes. The transfer of data between nodes

is software transparent, so no I/O overhead is required.

Transmit and Receive FIFOs buffer data during peak data

rates to optimize CPU and bus performance to maintain high

data throughput.

The Reflective Memory also allows interrupts to one or

more nodes by writing to a byte register. These interrupt (three

level, user definable) signals may be used to synchronize a

system process, or used to follow any data that may have

preceded it. The interrupt always follows the data to ensure the

reception of the data before the interrupt is acknowledged.

The VMIVME-5576 requires no initialization unless

interrupts are being used. If interrupts are used, vectors and

interrupt levels must be written to on-board registers and the

interrupts armed.

Each node on the system has a unique identification

number between 0 and 255. The node number is established

during hardware system integration by placement of jumpers

on the board. This node number can be read by software by

accessing an on-board register. In some applications, this node

number would be useful in establishing the function of the

node.

LINK ARBITRATION — The VMIVME-5576 system

is a fiber-optic daisy chain ring as shown in Figure 2. Each

transfer is passed from node to node until it has gone all the

way around the ring and reaches the originating node. Each

node retransmits all transfers that it receives except those that

it had originated. Nodes are allowed to insert transfers

between transfers passing through.

INTERRUPT TRANSFERS — In addition to

transferring data between nodes, the VMIVME-5576 will

allow any processor in any node to generate an interrupt on

any other node. These interrupts would generally be used to

indicate to the receiving node that new data has been sent and

is ready for processing. These interrupts are also used to

indicate that processing of old data is completed and the

receiving node is ready for new data.

Three interrupts are available. The user may define the

function, priority, and vector for each interrupt. Any

processor can generate an interrupt on any other node on the

network. In addition, any processor on the network can

generate an interrupt on all nodes on the network. Interrupts

are generated by simply writing to a single VMIVME-5576

register.

All data and interrupt command transfers contain the

node number of the node that originated the transfer. This

information is used primarily so the originating node can

remove the transfer from the network after the transfer has

traversed the ring. The node identification is also used by

nodes receiving interrupt commands. When a node receives

an interrupt command for itself, it places the identification

number of the originating node in a FIFO. Up to 512

interrupts can be stacked in the FIFO. During the interrupt

service routine, the identification of the interrupting node can

be read from the FIFO.

ERROR MANAGEMENT — Errors are detected by

the VMIVME-5576 with the use of the error detection

facilities of the TAXI chipset and additional parity encoding

and checking. The error rate of the VMIVME-5576 is a

function of the rate of errors produced in the optical portion

of the system. This optical error rate depends on the length

and type of fiber-optic cable.

Assuming an optical error rate of 10-12. the error rate of

the VMIVME-5576 is 10-10 transfers/transfer. However, the

rate of undetectable errors is less than 10-20 transfers/transfer.

When a node detects an error, the erroneous transfer is

removed from the system and a VMEbus interrupt is

generated, if armed.

The VMIVME-5576 can be operated in a redundant

transfer mode in which each transfer is transmitted twice. In

.jpg)

.jpg)

.jpg)

.jpg)

.png)

.jpg)

.jpg)

_lVjBYb.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)

.jpg)