GEMVME6100 Single-Board Computer Programmer’s Reference Guide

block diagram. The remainder of the chapter provides memory map

information including a default memory map, MOTLoad’s processor

memory map, a default PCI memory map, MOTLoad’s PCI memory map,

a PCI I/O memory map, and system I/O memory maps.

Note Programmable registers in the MV64360 system controller are

documented in a separate publication and obtainable from

Motorola Computer Group by contacting your Field Area

Engineer. Refer to Appendix A, Related Documentation, for

more information on obtaining this documentation.

Overview

The MVME6100 is a single-board computer based on the PowerPC

MPC7457 processor, the Marvell MV64360 system controller, up to 2 GB

of ECC-protected DDR DRAM, up to 128MB of Flash memory, a dual

Gigabit Ethernet interface, two asynchronous serial ports, and two

IEEE1386.1 PCI, PCI-X capable mezzanine card slots (PMCs

Memory Maps

Default Processor Memory Map

The MV64360 presents a default CPU memory map following RESET

negation. The following table shows the default memory map from the

point of view of the processor. Address bits [35:32] are only relevant for

the MPC7457 extended address mode and are not shown in the following

tables. (Note that it is the same as the GT-64260A with the addition of

integrated SRAM.)

ABORT_L

Abort. This bit reflects the current state of the onboard abort signal.

This is a debounced version of the abort switch and may be used to

determine the state of the abort switch. A set condition indicates that

the abort switch is not depressed while a cleared condition would

indicate that the abort switch is asserted.

FLASH_BSY_L

FLASH Busy. This bit provides the current state of the Flash Bank A

StrataFlash device Status pins. These two open drain output pins are

wire ORed. Refer to the appropriate Intel StrataFlash data sheet for a

description on the function of the Status pin.

FUSE_STAT

Fuse Status. This bit indicates the status of the onboard fuses. A

cleared condition indicates that one of the fuses is open. A set

condition indicates that all fuses are functional.

SROM_INIT

SROM Init. This bit indicates the status of the SROM Init. A cleared

condition indicates that the SROM Init is disabled. A set condition

indicates that the SROM Init is enabled and the MV64360 was

initialized using the MV64360 User Defined Initialization SROM at

$A6.

TSTAT_MASK

Thermostat Mask. This bit is used to mask the DS1621 temperature

sensor thermostat output. If this bit is cleared, the thermostat output

will be enabled to generate an interrupt on GPP3. If the bit is set, the

thermostat output is disabled from generating an interrupt.

FBOOTB_WP

Software Flash Bank B Boot Block Write Protect. This bit is to provide

software-controlled protection against inadvertent writes to the Flash

Bank B Top 1 MB (0xFFF00000) space. Clearing this bit and disabling

HW write-protect will enable writes to the Bank B Flash Top 1MB

boot block devices. This bit is set during reset and must be reset by the

system software to enable writing of the Flash Bank B boot block.

FBA_WP_HDR

Hardware Flash Bank A write protect header status. Read ONLY.

Hardware jumper configuration can not be overridden by the software

control bit 6 in this register.

FBOOTB_WP_HDR

Hardware Flash Bank B Boot Block write protect header status. Read

ONLY. Hardware jumper configuration can not be overridden by the

software control bit 3 in this register.

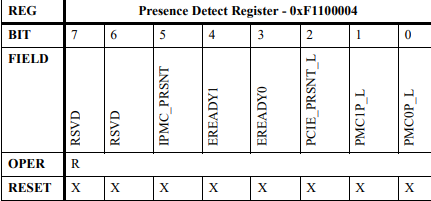

IPMC_PRSNT

IPMC Module Present. If set (HIGH true), there is PMCspan module

installed. If cleared, the PMCspan module is not installed.

EREADY1

EREADY1. Indicates that the PrPMC module installed in PMC slot 2

is ready for enumeration when set. If cleared, the PrPMC module is not

ready for enumeration. The PrPMC software must assert EREADY#

for this bit to be set. The purpose of EREADY# is to provide a

signaling method indicating that a non-monarch (vassal) PrPMC is

ready to be enumerated.

EREADY0

EREADY0. Indicates that the PrPMC module installed in PMC slot 1

is ready for enumeration when set. If cleared, the PrPMC module is not

ready for enumeration. The purpose of EREADY# is to provide a

signaling method indicating that a non-monarch (vassal) PrPMC is

ready to be enumerated.