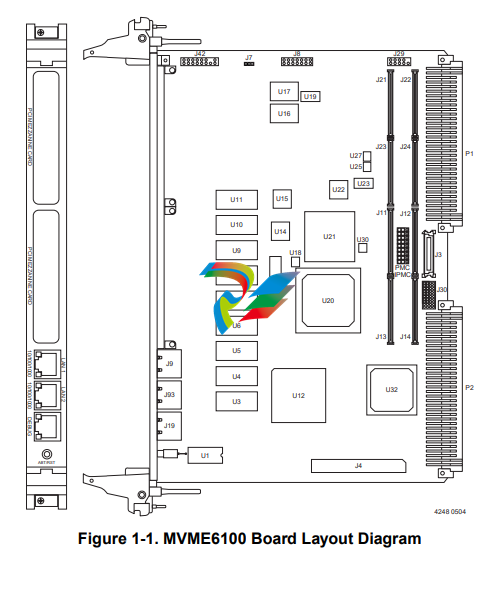

EMERSONMVME6100 Single-Board Computer Programmer’s Reference Guide

block diagram. The remainder of the chapter provides memory map

information including a default memory map, MOTLoad’s processor

memory map, a default PCI memory map, MOTLoad’s PCI memory map,

a PCI I/O memory map, and system I/O memory maps.

Note Programmable registers in the MV64360 system controller are

documented in a separate publication and obtainable from

Motorola Computer Group by contacting your Field Area

Engineer. Refer to Appendix A, Related Documentation, for

more information on obtaining this documentation.

Overview

The MVME6100 is a single-board computer based on the PowerPC

MPC7457 processor, the Marvell MV64360 system controller, up to 2 GB

of ECC-protected DDR DRAM, up to 128MB of Flash memory, a dual

Gigabit Ethernet interface, two asynchronous serial ports, and two

IEEE1386.1 PCI, PCI-X capable mezzanine card slots (PMCs).

The following table lists the features of the MVME6100.

Table 1-1. MVME6100 Features Summary

Feature Description

Processor – Single 1.3 GHz MPC7457 processor

– Bus clock frequency at 133 MHz

– 36-bit address, 64-bit data buses

– Integrated L1 and L2 cache

L3 Cache – 2MB using DDR SRAM

– Bus clock frequency at 211 MHz

Flash – Two banks (A & B) of soldered Intel StrataFlash devices

– 8 to 64MB supported on each bank

– Boot bank is switch selectable between banks

– Bank A has combination of software and hardware write-protect

scheme

– Bank B top 1MB block can be write-protected through

software/hardware write-protect control

System Memory – Two banks on board for up to 2GB using 256Mb or 512Mb

devices

– Bus clock frequency at 133 MHz

Memory Controller

PCI Host Bridge

Dual 10/100/1000 Ethernet

Interrupt Controller

PCI Interface

I

2

C Interface

– Provided by Marvell MV64360 system controller

NVRAM

Real-Time Clock

Watchdog Timer

– 32KB provided by MK48T37

On-board Peripheral

Support

– Dual 10/100/1000 Ethernet ports routed to front panel RJ-45

connectors, one optionally routed to P2 backplane

– Two asynchronous serial ports provided by an ST16C554D; one

serial port is routed to a front panel RJ-45 connector and the second

serial port is optionally routed to the P2 connector for rear I/O or

on-board header

Table 1-1. MVME6100 Features Summary (continued)

Feature Description

PCI/PMC – Two 32/64-bit PMC slots with front-panel I/O plus P2 rear I/O as

specified by IEEE P1386

– 64-bit slots; 33/66 MHz PCI or 66/100 MHz PCI-X

VME Interface – Tsi148 VME 2Esst ASIC provides:

❏ Eight programmable VMEbus map decoders

❏ A16, A24, A32, and A64 address

❏ 8-bit, 16-bit, and 32-bit single cycle data transfers

❏ 8-bit, 16-bit, 32-bit, and 64-bit block transfers

❏ Supports SCT, BLT, MBLT, 2eVME, and 2eSST protocols

❏ 8 entry command and 4KB data write post buffer

❏ 4KB read ahead buffer

PMCspan Support – One PMCspan slot

– Supports 33/66 MHz, 32/64-bit PCI bus

– Access through PCI6520 bridge to PMCspan

Form Factor – Standard 6U VME

Miscellaneous – Combined reset and abort switch

– Status LEDs

– 8-bit software-readable switch

– VME geographical address switch

Memory Maps

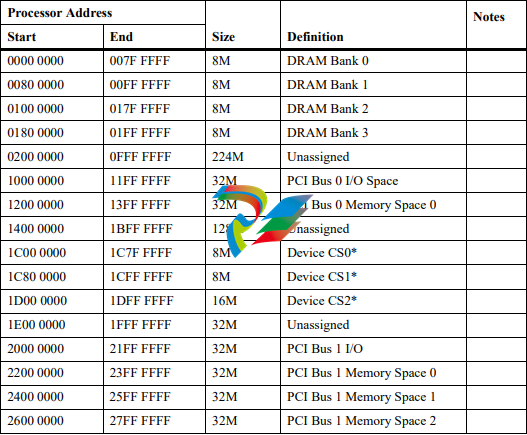

Default Processor Memory Map

The MV64360 presents a default CPU memory map following RESET

negation. The following table shows the default memory map from the

point of view of the processor. Address bits [35:32] are only relevant for

the MPC7457 extended address mode and are not shown in the following

tables. (Note that it is the same as the GT-64260A with the addition of

integrated SRAM.)

Table 1-2. Default Processor Address Map

ABORT_L

Abort. This bit reflects the current state of the onboard abort signal.

This is a debounced version of the abort switch and may be used to

determine the state of the abort switch. A set condition indicates that

the abort switch is not depressed while a cleared condition would

indicate that the abort switch is asserted.

FLASH_BSY_L

FLASH Busy. This bit provides the current state of the Flash Bank A

StrataFlash device Status pins. These two open drain output pins are

wire ORed. Refer to the appropriate Intel StrataFlash data sheet for a

description on the function of the Status pin.

FUSE_STAT

Fuse Status. This bit indicates the status of the onboard fuses. A

cleared condition indicates that one of the fuses is open. A set

condition indicates that all fuses are functional.

SROM_INIT

SROM Init. This bit indicates the status of the SROM Init. A cleared

condition indicates that the SROM Init is disabled. A set condition

indicates that the SROM Init is enabled and the MV64360 was

initialized using the MV64360 User Defined Initialization SROM at

$A6.