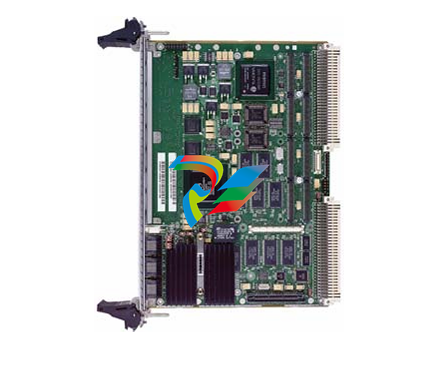

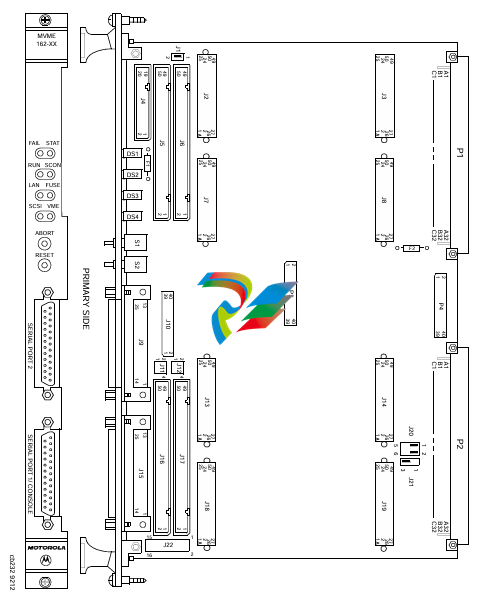

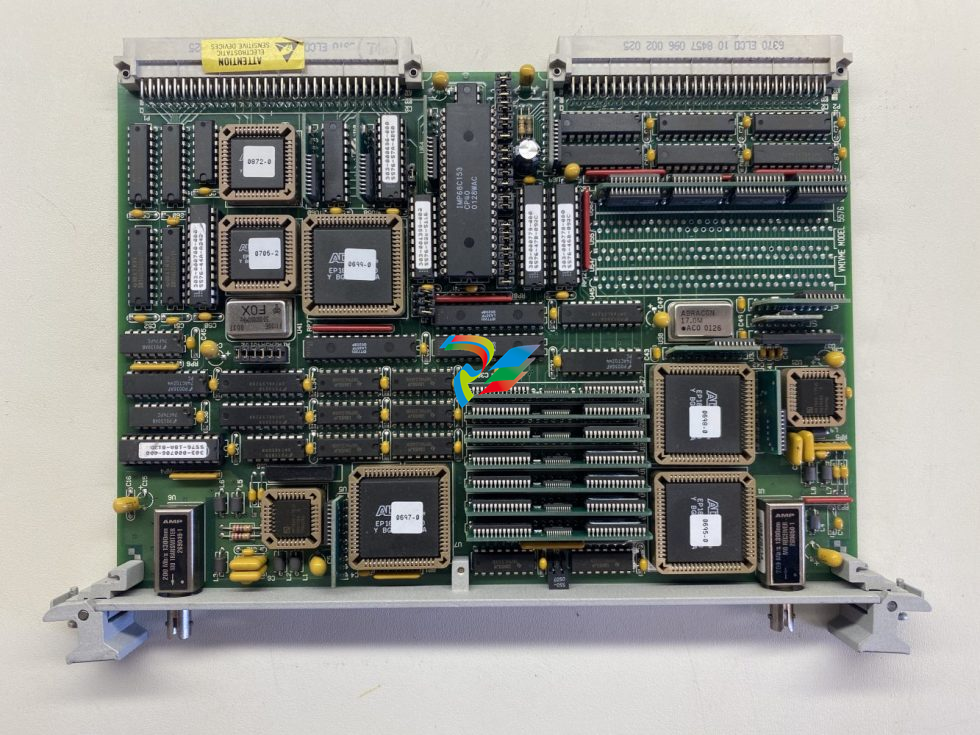

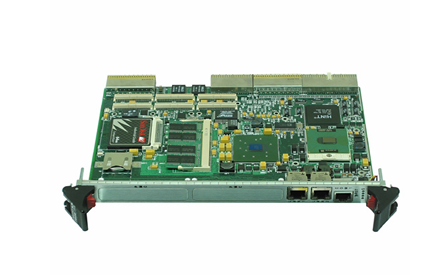

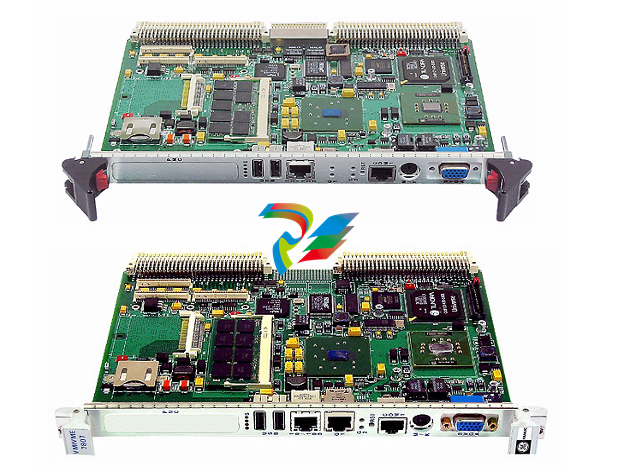

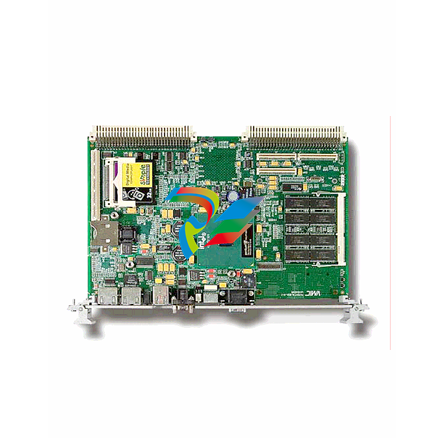

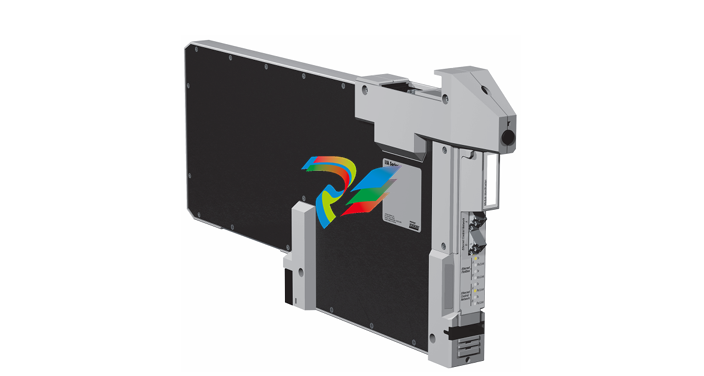

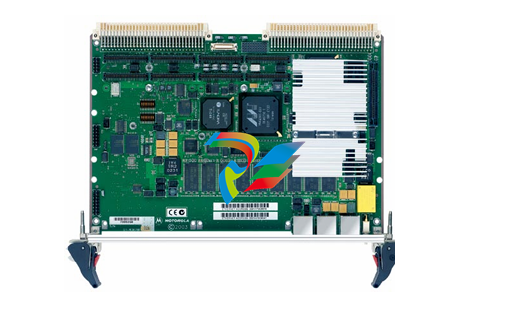

SST SST-PB3-VME-1 and SST-PB3-VME-2 Interface card

SST SST-PB3-VME-1 and SST-PB3-VME-2 Interface card

Host Register Layout

Each channel has its own set of registers, located in short I/O space. The base I/O address is set

via the switch

ost Register Layout

The following “offsets” are offsets from the base address. A capital “X” means that the bit is

reserved (writing to it will result in undefined behavior).

Short I/O Registers

The card contains the following short I/O registers.

3.3.1 Control Register

This register is a group of control and status bits.

Each channel has four interrupt flags, two for use in each direction. Setting CardIrq1 or CardIrq0

generates an interrupt to the card with the relevant flag set. When HostIrq1 OR HostIrq0 is '1'

and IntEn is '1', the card drives the IRQ pin (as set by the DIP switch).

One flag could be used for a command interface, and another for changing I/O data.

The firmware module dictates how these flags are used. If the module uses only one flag,

it will be Flag 0.

Bit Name Description

CardRun This bit controls and indicates whether or not the card’s processor is running.

• When this bit is 0. the processor is halted.

• When this bit is 1. the processor is running normally.

• When this bit is 1. and watchdog has timed out, processor is halted.

This bit must remain low for at least 50 µs to guarantee proper reset.

MemEn High (1) enables shared memory decoding of addresses in this board’s range. This board’s

range is defined by the AddrMatch Register.

IntEn High (1) enables interrupts on IrqLevel when a HostIrq bit is high (1).

• Writing 1 enables interrupts

• Writing 0 disables interrupts (the IrqPending flag still functions as described)

WdTout WdTout high (‘1’) indicates that a watchdog timeout has occurred, or that the CPU has been

held in RESET by some other means. To restore this bit to 0. clear CardRun.

HostIrq1 • This bit is used by the card processor to send interrupts to channel 1 of the host

• Writing 1 acknowledges the interrupt and clears it

• Writing 0 has no effect

• Reading 1 indicates interrupt in progress

• Reading 0 indicates interrupt complete

HostIrq0 • This bit is used by the card processor to send interrupts to channel 0 of the host

• Writing 1 acknowledges the interrupt and clears it

• Writing 0 has no effect

• Reading 1 indicates interrupt in progress

• Reading 0 indicates interrupt complete

CardIrq1 This bit is used by the host to send interrupts to channel 1 of the card processor

• Writing 1 generates an interrupt to the card

• Writing 0 has no effect

• Reading 1 indicates interrupt in progress

• Reading 0 indicates interrupt complete

CardIrq0 This bit is used by the host to send interrupts to channel 0 of the card processor

• Writing 1 generates an interrupt to the card

• Writing 0 has no effect

• Reading 1 indicates interrupt in progress

• Reading 0 indicates interrupt complete

AddrMatch Register

This register controls the base memory address of the channel in host memory space.

Each channel may be at a different address. If two channels are used at the same address, use

MemEn to turn on one channel at a time.

Bank Address Register

This register is used to switch banks of shared memory into host memory space.

Table 19: Bank Address Register Values

In this table, the default values are highlighted.

HostIrq ID Register

This register contains an 8-bit IrqLevel ID value written by the host to distinguish the card from

other devices that might share the same IRQ level (as set by the DIP switch). This ID is placed

on the VME bus during an interrupt acknowledge cycle by the device that generated an IRQ to

the host.

3.3.6 LedReg Register

This register reflects the state of card LEDs, allowing host software to monitor the LEDs and

display them on-screen.

The LedReg register represents the state of the card LEDs. The state of this register is controlled

by firmware. Reading the register will reflect the following LED states:

Debug Register

This register is reserved for future use.

3.3.8 HDR Register

This HDR register can be used to pass 1 byte of data from card to host. The use of this register is

determined by firmware/boot code, and boot code power-on reset value is 0x41.

3.3.9 VMEReg Register

The VME register is used for VME-specific functions and only contains the VME SysFail bit at

this time.

The Sysfail LED is directly controlled by the SysFail bit in this register. If this bit is set to a logic

'1', the LED will turn red, which indicates a VME system error. It also will assert the VME

System failure signal on the backplane.

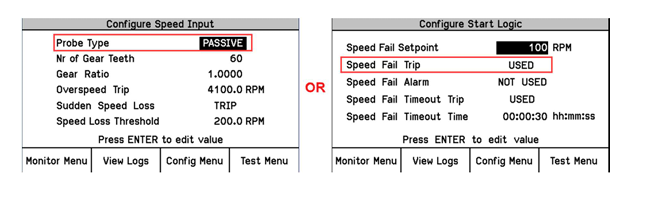

Serial Port

The card’s serial port allows the network configuration file and firmware module to be

transferred to flash, and for named firmware to start automatically on reset.

The following sections describe the serial port’s operation.

A.1.1 Connecting to the Serial Port

The serial cable for a standard PC COM port must have lines 2 and 3 swapped. No handshaking

is required. Pins 2 and 3 are wired the same as a PC 9-pin COM port.

Connect to the serial port using any communication software (such as Hyper terminal). The

serial port defaults to 115200 with no parity, 8 data bits and 1 stop bit. Baud rates from 9600 to

115 Kbaud can be set in Boot.ini. Pressing any key within 3 seconds (default value) of a channel

reset will enter serial communication mode.

Card Errors

The following errors may be reported during the card’s startup self-test.

A.2.1 HDR Messages

If HDR reads anything other than 0x41. the card hasn’t been found. To fix the problem, follow

these steps:

1. Double-check the switch settings and make sure they match up with the I/O driver port

address setting in the software application.

2. Make sure you have waited up to 2 seconds after the channel reset has been negated

before trying to access it.

3. Check for an I/O conflict.

| REXROTH | SL36 |

| REXROTH | VT3000S34-R5 |

| REXROTH | VT3006S34R5 |

| REXROTH | VT3006S35R1 |

| REXROTH | VT-VSPA1-1-11 |

| Rexroth | R911259395 |

| REXROTH | TV 3000HT PUMF |

| REXROTH | MSK030C-0900-NN-M1-UP1-NSNN |

| REXROTH | MSK060C-0600-NN-M1-UP1-NSNN |

| REXROTH | MSK050C-0600-NN-M1-UP1-NSNN |

| REXROTH | MSK070C-0150-NN-S1-UG0-NNNN |

| REXROTH | MSK070D-0450-NN-M1-UP1-NSNN |

| REXROTH | VDP40.2BIN-G4-PS-NN |

| REXROTH | VT3002-2X/48F |

| User name | Member Level | Quantity | Specification | Purchase Date |

|---|